# InP DHBT Optimization for mm-Wave Power Applications

Virginio Midili

Kongens Lyngby 2017

Technical University of Denmark Department of Electrical Engineering Ørsteds Plads, building 348, 2800 Kongens Lyngby, Denmark Phone +45 45 25 38 00 elektro@elektro.dtu.dk www.elektro.dtu.dk

# Abstract

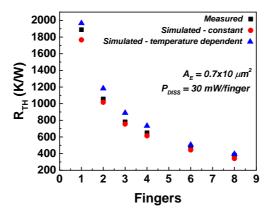

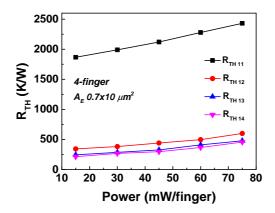

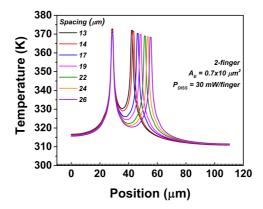

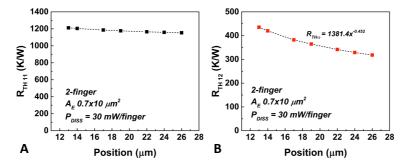

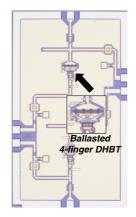

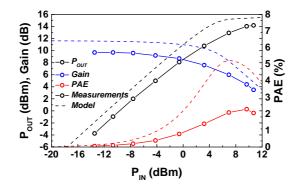

This work presents the optimization of an InP Double Heterojunction Transistor (DHBT) technology for Power Amplifier (PA) applications in the millimeterwave frequency range. Starting from an existing InP DHBT technology for high-speed mixed-signal applications, the epitaxial structure of a single-finger DHBT has been designed to fulfill the requirements set for the design of the power cell in terms of maximum cutoff frequency  $f_{MAX}$  and breakdown voltage  $BV_{CEO}$ . A 2D TCAD modeling approach is proposed to investigate device high-frequency performances for different collector structures. The static and high-frequency performances of devices with different geometrical layout dimensions have been investigated to select the unit finger device with  $0.7 \times 10 \ \mu m^2$ emitter area having  $f_{MAX} = 400$  GHz and  $BV_{CEO} > 7$  V for the unit power cell. Single-finger devices are combined in multi-finger structures to increase total output power. The electrical performances of multi-finger devices are investigated with respect to number of fingers and geometrical dimensions. The thermal characterization of multi-finger devices is performed to understand the impact of self and mutual-heating. An approach based on 3D thermal simulations of multi-finger devices is proposed to study heating effects and to extract thermal parameters for the device large-signal model. A 4-finger device with  $0.7 \times 10 \ \mu m^2$  unit finger emitter area is finally selected for the PA power cell. The 4-finger device has  $f_{MAX} = 370$  GHz and can deliver  $P_{OUT} = 16$  dBm to an optimal load under class-A operation. As a further improvement to reduce thermal effects in multi-finger devices, the ballasting resistor approach is investigated. The performances of DHBTs with different ballasting resistor networks are compared in terms of static and high-frequency performances. A ballasting solution is finally proposed as a trade-off between the improvement in device Safe Operating Area (SOA) and the degradation of high-frequency performances.

# Resumé

Dette arbejde præsenterer optimeringen af en InP Double Heterojunction Transistor (DHBT) teknologi til anvendelse indenfor effektforstærkere i millimeterbølgefrekvensområdet. En eksisterende epitaksial struktur for en enkelt-finger InP DHBT er til at begynde med blevet designet om med henblik påat møde krav opsat til en enkelt effektcelle i term af maksimum afskæringsfrekvens, fmax, og nedbrudsspænding, BV<sub>CEO</sub>. En 2D TCAD modelleringsmetode er formuleret for at undersøge transistorens højfrekvensegenskaber som funktion af forskellige kollektorstrukturer. Statiske og højfrekvensegenskaber for transistorer med forskellige geometriske layout dimensioner er blevet undersøgt for at udvælge en transistor med f<sub>MAX</sub> = 400 GHz og BV<sub>CEO</sub> > 7 V til brug i den enkelte effektcelle.

Enkelt-finger transistorer er blevet kombineret til flerfingre transistorer for at øge udgangseffekten. De elektriske egenskaber af flerfingre transistorer er undersøgt med hensyn til antal finger og geometriske dimensioner. Termisk karakterisering af flerfingre transistorer er udført for at forståeffekten af selv- og gensidig opvarmning. En metode baseret på3D termiske simulationer af flerfingre transistorer foreslås her til studium af opvarmningseffekter og for at ekstrahere termiske parameters til brug i storsignal modellering af transistoren. En 4-finger transistor med  $0.7 \times 10 \ \mu m^2$  emitter areal per finger er endeligt blevet udvalgt til brug som enhedscellen i en effektforstærker. 4-finger transistoren har  $f_{MAX} = 370 \text{ GHz}$  og kan levere  $P_{OUT} = 16 \text{ dBm}$  til en optimal belastning under klasse-A operation. Som en yderligere forbedring til at reducere termiske effekter i flerfingre transistorer er en metode med ballast modstande undersøgt. DHBT'er med forskellige ballast modstande er sammenlignet med hensyn til deres statiske- og højfrekvensegenskaber. Endeligt er en ballast løsning forslået som et trade-off mellem forbedringer i "Safe Operation Area (SOA)" og forringelse i højfrekvensegenskaberne.

# Preface

The PhD study presented in this thesis was carried out in collaboration between III-V Lab and the Electromagnetic Systems (EMS) group at the department of Electrical Engineering at the Technical University of Denmark (DTU) between September 2014 and December 2017. This work is part of the EU project "InP DHBT Optimization for mm-Wave Power Applications" (IN-POWER) within FP7. Financial support was provided by the European Union through a Marie-Curie ITN EID fellowship.

The project supervisor is Associate Professor Tom Keinicke Johansen from DTU while Dr. Virginie Nodjiadjim acted as industrial supervisor.

Kongens Lyngby, Denmark, December 2017

Virginio Midili

# Acknowledgements

I feel deeply grateful towards a number of people for their support during my PhD studies both at DTU and at III-V Lab.

First and foremost, I want to thank my supervisors Prof. Tom K. Johansen and Dr. Virginie Nodjiadjim for their guidance, their supervision and their encouragement during these three years. In addition to scientific and technical supervisions, I feel blessed to have had them as a constant example of rigour and passion for research work.

I also want to thank all the people involved in the IN-POWER project: Muriel Riet for the invaluable work and knowledge on DHBT fabrication at III-V Lab, Jean-Yves Dupuy and Agnieszka Konczykowska for providing top-notch insights on research methods and circuit design issues. Many thanks also to Filipe Jorge and Fabrice Blache for their precious help and advice about characterization issues. Last but not least, I want to thank the other fellow student of the IN-POWER project, Michele Squartecchia who shared with me the ups and downs of PhD life in these three years.

Besides the people I had the opportunity to work closely with, I would like to thank all the researchers and staff members of DTU and III-V Lab, especially the PhD students of both institutions that I had the opportunity to meet. The informal discussions, the sharing of ideas and the kind support contributed to my journey and enriched me beyond the scope of my PhD project.

Finally, I want to thank my family and my friends for supporting me through all these three years as they have always done.

v

# Contents

| A        | bstra           | act                                      | i   |

|----------|-----------------|------------------------------------------|-----|

| R        | $\mathbf{esum}$ | ié                                       | ii  |

| P        | refac           | e                                        | iii |

| A        | cknov           | wledgements                              | iv  |

| 1        | App             | plications and context                   | 1   |

|          | 1.1             | Applications of mm-wave circuits         | 1   |

|          | 1.2             | State-of-the-art for mm-wave transistors | 5   |

|          | 1.3             | Objectives of this work                  | 6   |

| <b>2</b> | Sing            | gle finger InP DHBT optimization         | 8   |

|          | 2.1             | Baseline device structure                | 8   |

|          | 2.2             | Characterization of single-finger DHBT   | 11  |

|          |                 | · · ·                                    | 12  |

|          |                 |                                          | 13  |

|          | 2.3             | ·                                        | 19  |

|          |                 | - •                                      | 20  |

|          |                 |                                          | 22  |

|          |                 | -                                        | 24  |

|          |                 |                                          | 26  |

|          | 2.4             | -                                        | 34  |

|          |                 |                                          | 37  |

|          |                 |                                          | 44  |

|          |                 | - *                                      | 45  |

|          | 2.5             | -                                        | 48  |

| 3        | Mu    | lti-finger InP DHBTs for mm-wave Power Amplifiers            | 50  |

|----------|-------|--------------------------------------------------------------|-----|

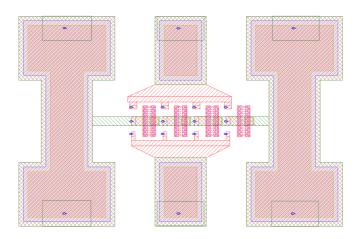

|          | 3.1   | Device description                                           | 51  |

|          | 3.2   | Characterization of multi-finger DHBTs                       | 51  |

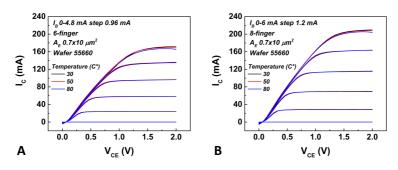

|          |       | 3.2.1 DC measurements                                        | 51  |

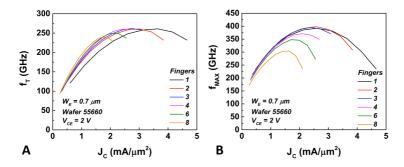

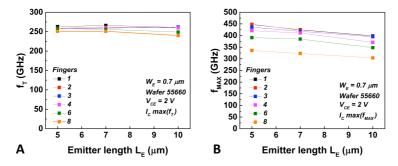

|          |       | 3.2.2 High frequency measurements                            | 54  |

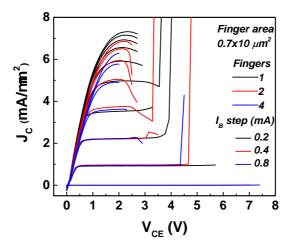

|          |       | 3.2.3 Safe Operating Area analysis                           | 57  |

|          | 3.3   | Thermal behavior of multi-finger DHBTs                       | 59  |

|          |       | 3.3.1 Characterization                                       | 59  |

|          |       | 3.3.2 3D thermal simulations                                 | 64  |

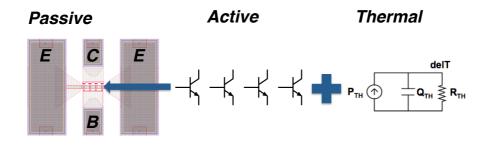

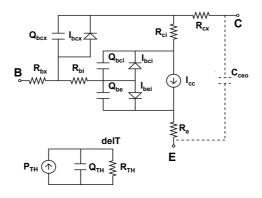

|          | 3.4   | Electro-thermal model of multi-finger DHBT                   | 71  |

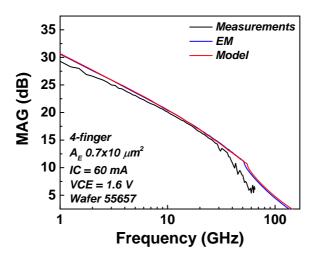

|          |       | 3.4.1 EM simulation                                          | 71  |

|          |       | 3.4.2 Large-signal single-finger model                       | 72  |

|          |       | 3.4.3 Thermal network                                        | 74  |

|          |       | 3.4.4 Results of large-signal model                          | 75  |

|          | 3.5   | Conclusions                                                  | 79  |

| 4        | Imr   | provement of multi-finger InP DHBT Safe Operating Area       | 81  |

| 4        | 4.1   | Overview of SOA improvement techniques                       | 81  |

|          | 4.1   | 4.1.1 Material approach                                      | 82  |

|          |       | 4.1.1     Material approach       4.1.2     Thermal approach | 82  |

|          |       | 4.1.3 Electrical approach: ballasting                        | 83  |

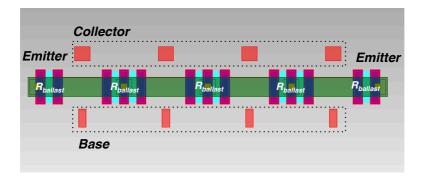

|          | 4.2   | Impact of ballasting on DHBT performance                     | 84  |

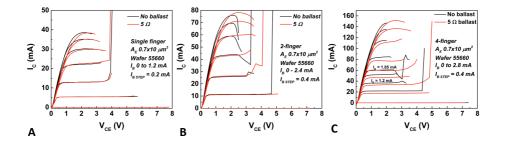

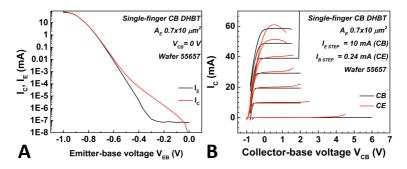

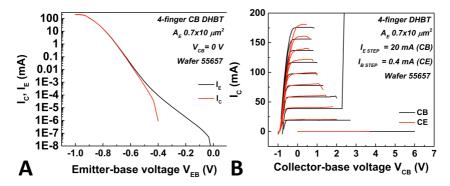

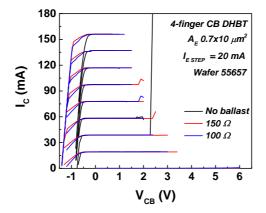

|          | 1.2   | 4.2.1 Static performance                                     | 84  |

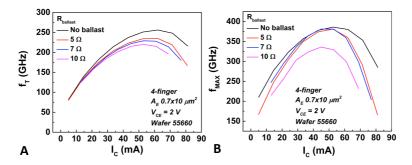

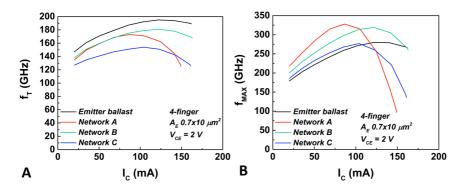

|          |       | 4.2.2 Frequency performance                                  | 87  |

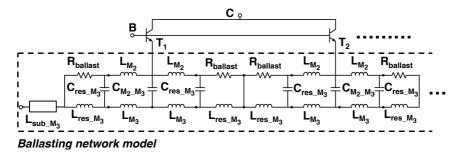

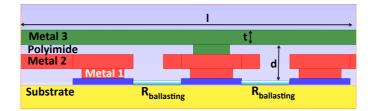

|          | 4.3   | EM and lumped parameters modeling                            | 88  |

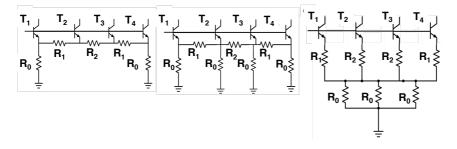

|          | 4.4   | Alternative ballasting topologies                            | 91  |

|          | 1.1   | 4.4.1 Static performances                                    | 93  |

|          |       | 4.4.2 Frequency performances                                 | 95  |

|          | 4.5   | DHBT in common-base configuration                            | 98  |

|          | 4.6   |                                                              | 102 |

|          | -     |                                                              |     |

| <b>5</b> | Cire  | 1                                                            | 103 |

|          | 5.1   |                                                              | 103 |

|          | 5.2   |                                                              | 105 |

|          | 5.3   | Two-stacked transistor with ballasted common-base            | 106 |

| 6        | Cor   |                                                              | 108 |

|          | 6.1   | Summary of Results                                           | 108 |

|          | 6.2   |                                                              | 110 |

| A        | Ap    | pendix A                                                     | 112 |

| Bi       | blios | graphy                                                       | 124 |

|          | 8     |                                                              |     |

# Glossary

#### Acronyms

- AC Alternating current

- BGN Bandgap Narrowing

- CB Common base

- CE Common emitter

- DC Direct current

- DD Drift-Diffusion

- DHBT Double Heterojunction Bipolar Transistor

- EB Energy balance

- EHF Extremely High Frequency

- FEM Finite Element Model

- GSG Ground-Signal-Ground

- HBT Heterojunction Bipolar Transistor

- HD Hydrodynamic model

- MAG Maximum available gain

- MMIC Monolithic Microwave Integrated Circuit

- PA Power Amplifier

#### CONTENTS

- PAE Power Added Efficiency

- SDD Symbolically Defined Device

- SEM Scanning Electron Microscope

- SOA Safe Operating Area

- SOLT Short-Open-Load-Through calibration

- SRH Shockley-Read-Hall

- TCAD Technology Computer-Aided Design

- UCSD University California San Diego large-signal model

- VNA Vector Network Analyzer

#### Symbols

- lpha Current transfer ratio I<sub>C</sub> /I<sub>E</sub>

- $\beta$  Current transfer ratio I<sub>C</sub> /I<sub>B</sub>

- $\epsilon$  Dielectric permittivity

- $\mu$  Carrier mobility

- $\phi$  Thermal-electric feedback coefficient

- $\tau_{\rm b}$  Base-transit time

- $\tau_{\rm c}$  Collector transit time

- $A_E$  Emitter contact area

- $D_n$  Electrons diffusion coefficient

- $E_{C}$  Conduction band energy

- $E_{\rm F}$  Fermi level

- $E_G$  Energy bandgap

- E<sub>T</sub> Trap energy level

- $E_V$  Valence band energy

- g<sub>m</sub> Transconductance

- h<sub>21</sub> Short-circuited current gain

- $J_C$  Collector current density

| $N_{d}$                     | Doping concentration                                        |

|-----------------------------|-------------------------------------------------------------|

| $\mathrm{R}_{\mathrm{TH}}$  | Thermal resistance                                          |

| $X_d$                       | Depletion region width                                      |

| $BV_{CBC}$                  | <sup>D</sup> Breakdown voltage in common-base configuration |

| $BV_{CEC}$                  | Common emitter breakdown voltage                            |

| ${\rm f}_{\rm MAX}$         | Maximum oscillating frequency                               |

| $f_{\rm T}$                 | Cutoff frequency                                            |

| $I_{\rm B}$                 | Base current                                                |

| $I_{\rm C}$                 | Collector current                                           |

| $I_{\rm E}$                 | Emitter current                                             |

| $\mathrm{V}_{\mathrm{BE}}$  | Base-emitter voltage                                        |

| $\mathrm{V}_{\mathrm{CB}}$  | Collector-base voltage                                      |

| $\mathrm{V}_{\mathrm{CE}}$  | Collector-emitter voltage                                   |

| $\mathbf{v}_{\mathrm{sat}}$ | Carrier saturation velocity                                 |

| k                           | Boltzmann constant                                          |

| U                           | Mason's unilateral gain                                     |

\_\_\_\_

# Chapter 1

# **Applications and context**

# 1.1 Applications of mm-wave circuits

The range of radio frequencies between 30 and 300 GHz is designated as Extremely High Frequency (EHF) by the International Telecommunication Union (ITU). Radio waves in this interval have free-space wavelength between 10 and 1 mm thus frequencies in this range are commonly referred as millimeter wave (mm-wave) frequencies. The attenuation for propagating waves in this interval is severe due to absorption by gases in the atmosphere. They have therefore a short range and they are mostly suitable for terrestrial communication.

The mm-wave spectrum was traditionally reserved to military and scientific applications. As the demand for bandwidth continues to grow due to the increased utilization and number of connected devices, this range is slowly being allocated for consumer and commercial applications.

There are several advantages and drawbacks related to the utilization of the mm-wave spectrum. The main advantages in moving up to higher frequencies are mainly related to bandwidth and the size of antenna components.

The large available bandwidth translates directly to higher data-rates that can support high-quality video streaming and other bandwidth intensive applications or simply to increase the capacity of current network connections. For a fixed gain, the size of an antenna working in the mm-wave range is reduced leading to smaller and more compact equipment. In addition, the narrower beam of a mm-wave antenna allows to achieve greater resolutions. As the propagation range of mm-waves is rather small, communication systems with increased security and immunity to jamming can be designed.

The obstacles in moving applications to the mm-wave spectrum are related to the short range and the cost of the underlying technology. Due to the high atmospheric attenuation, mm-waves have very short transmission range as mentioned above. This range is reduced even more with fog, rain and moisture [1] Increasing this range requires the design of high power transmitters and highgain antennas along with high-sensitivity receivers. In this way, the trasmission range can be normally increased to about 1 kilometer. However, mm-wave applications require line-of-sight operations as physical objects are blocking obstacles for waves in this range. Besides physical limitations, technological challenges exist to manufacture semiconductor circuits able to generate, amplify, transmit and receive mm-wave signals.

In the past decades, the research focused on designing and improving transistors that could operate at mm-wave frequencies. Several material systems and device designs have been investigated that are suitable for mm-wave applications with different characteristics. Manufacturers are currently able to provide technological platforms that allow the fabrication of Monolithic Microwave Integrated Circuits (MMICs) based on the different technologies at affordable costs, thanks to the increasing demand.

A wide range of applications exists already exploiting the advantages offered by circuits operating at mm-wave frequencies. Besides traditional scientific and military applications there is an increasingly growing number of commercial applications. Among these, single-chip short-range radars, healthcare and imaging applications and telecommunications applications are more widespread and will be described in the following sections.

## Scientific and military

The main scientific application of mm-wave circuits is in the astronomy and space domain and for example in the U.S. this band is commonly allocated for radio astronomy and remote sensing applications. Ground-based radio astronomy is limited to high altitude sites due to atmospheric absorption issues. Satellite-based remote sensing near 60 GHz can determine temperature in the upper atmosphere by measuring radiation emitted from oxygen molecules that is a function of temperature and pressure. For example, passive frequency allocation at 57-59.3 GHz is used for atmospheric monitoring in meteorological and climate sensing applications, and is important for these purposes due to the properties of oxygen absorption and emission in Earth's atmosphere. Currently operational U.S. satellite sensors and special sensor microwave/imager make use

of this frequency range [2].

#### **Mm-wave radars**

Mm-wave radars have fine resolution that makes them ideal for detecting small movements and objects and allows position determination with millimeter precision. In particular, radars in the 76 to 81 GHz frequency range are widely used in vehicle control and safety devices [3] [4]. The specific applications include sensors for automatic braking, lane intrusion, applications blind spot detection, forward collision detection, cruise control, and more. The radar chipset has a detection range of between 20 and 200 meters and customizable to perform various automotive applications. In-building radars are also used in military and public safety domain. Short range mm-wave radar is used also for ground penetration applications such as mine detection. Radar-like systems at mm-wave are commonly employed also in manufacturing process control. For example, flow measurement of fluids or slurries carrying solid materials or detection systems for undesired materials. Since mm-wave radar are non-optical systems they are employed with optically opaque materials as in the case of pipes and plenums and in the presence of dust and smoke. Among these applications there is level sensing in large tanks such as those found at petroleum refineries and distribution sites.

## Imaging

Imaging applications are an extension of radar that are interesting at mm-wave because of high-resolution. Mm-wave imaging systems employing interferometry and holographic techniques can obtain results comparable to X-ray type investigation without the use of ionizing radiation [5] [6]. Holographic techniques can use the reconstructed wavefront to view and analyze the image from multiple observation points simultaneously. Resolution is greatly enhanced when used in combination with multi-frequency or ultra-wide band (UWB) techniques. Existing applications range from scanning baggage for security to ground-penetrating imaging at archaelogical sites. Even if radar scanning is commonly used in the mm-wave spectrum, there is a great interest in passive scanning techniques. Two types of mm-wave imaging are commonly employed using general illumination with a mm-wave source and the utilization of the thermal radiation naturally emitted by the scanned item. In both cases similar radiometric detectors are employed as mm-wave camera. These mm-wave imaging systems can be used to detect concealed objects including ceramic materials and the presence of persons through non-metallic walls. Also, the absorption properties of mm-wave through

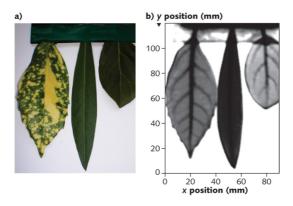

water and moisture can be exploited for the imaging of biological structures as shown in Fig. 1.1. Other applications currently being developed include cloud

Figure 1.1: Detected image at 300 GHz and visible counterpart [6].

imaging for weather research, high-resolution artificial vision for autonomous agents and aerial terrain mapping where high penetration through vegetation is needed.

## High-speed data links

#### **Mixed-signal**

Probably the most significant application of mm-wave transistors in terms of commercial demand is for front-end high-speed circuits in the telecommunication sector. Although short range wireless systems are a straightforward use case, high-speed transistors are employed also in front-end sub-systems for wired communication on fiber. The high frequencies capabilities of the devices are well suited to achieve gigabit data rates using increasingly complex wide bandwidth modulation schemes. Circuits based on mm-wave devices can be found in transceiver sub-systems for ADC and DAC components at high-data rates and as drivers for the modulation of optoelectronic components [7].

#### Wireless link

Future high-speed wireless communication is likely to take place at E-band and higher millimeter-wave frequencies. For communication systems at mm-waves, PA with large output powers are needed to extend the transmission distance of the wireless communication link. Given the ever growing demand for wide bandwidths and the continuous downscaling of devices, it becomes more and more difficult to obtain decent level of power at the transmitter end. InP DHBT technology has emerged as a very promising choice for high-frequency applications and have demonstrated capability to operate in the sub-terahertz domain [8], [9], [10] (in [8] a DHBT with 130 nm wide emitter is presented with  $f_{MAX}$ > 1 THz and BV<sub>CEO</sub> = 3.5 V, in [9] GaAsSb is used as the base material for a DHBT that presents  $f_{MAX} > 700$  GHz and in [10]  $f_{MAX}$  is as high as 470 GHz while still showing  $BV_{CEO} = 12$  V). Although PA designs in the same frequency range have been proposed based on competing technologies such as GaN HEMTs and SiGe BiCMOS, InP DHBTs exhibit excellent power handling capability as a good compromise between high output power and frequency of operation. PA designs based on InP HEMTs have already been realized obtaining 427 mW of output power with PAE of 19% at 94 GHz [11]. Advancements in technology process allowed GaN based MMICs to be demonstrated operating at E-Band with 1.3 W of output power and PAE of 27% [12] and in the W-band with 3W/mm of output power and PAE of 27.8% [13]. Thanks to more mature technology process and corresponding reliability InP based HBTs remain however interesting for commercial products targeting E-band and higher frequencies. PA designs based on SiGe technology showed an output power of 22-dBm and PAE of 3.6% at 120 GHz [14]. Although the high operating frequency, SiGe technology provides lower output power density levels compared to InP based technology. For all of the mentioned reasons InP DHBT technology is a good candidate to build PAs for E-band and higher frequencies and several designs have already been demonstrated up to 0.67 THz [15][16].

## 1.2 State-of-the-art for mm-wave transistors

As it was mentioned above, several competing technologies exist that could fulfill the requirements for high-frequency and high-power applications at mm-waves. Table 1.1 presents a summary of the state-of-the-art transistor technologies for sub-THz applications. The summary includes vertical and planar single-finger devices based on InP, SiGe and GaN and presents relevant performance metrics for PA as cutoff frequency  $f_T$ ,  $f_{MAX}$  and  $BV_{CEO}$ . Although the device technology presented in this work has lower frequency performances than the most recent published results of deeply scaled InP DHBTs, it is important to evaluate these same performances with comparable emitter dimensions in order to assess the advantages and drawbacks of different epitaxial design approaches. The scaling of emitter junction width in InP/InGaAs DHBT is a needed step to

| [Reference] Year | Technology                                    | $\mathop{\rm f_T}_{\rm (GHz)}$ | $_{\rm (GHz)}^{\rm f_{\rm MAX}}$ | $\begin{array}{c} \mathrm{BV}_{\mathrm{CEO}} \\ \mathrm{(V)} \end{array}$ |

|------------------|-----------------------------------------------|--------------------------------|----------------------------------|---------------------------------------------------------------------------|

| [8] 2011         | $0.13 \times 2 \ \mu m^2$ InP DHBT            | 520                            | 1100                             | 3.5                                                                       |

| [17] 2013        | 20  nm GaN HEMT                               | 454                            | 444                              | 10                                                                        |

| [18] 2012        | 130  nm SiGe HBT                              | 300                            | 500                              | 1.6                                                                       |

| This work        | $0.7 \mathrm{x5} \ \mu \mathrm{m}^2$ InP DHBT | 267                            | 450                              | 7.5                                                                       |

Table 1.1: Summary of state-of-the-art transistors for sub-THz applications

Table 1.2: Published InP-based DHBTs performances by emitter width

| [Reference] Year | Emitter dimensions $(\mu m \times \mu m)$ | $\begin{array}{c} f_{\rm T} \\ ({\rm GHz}) \end{array}$ | $\begin{array}{c} f_{\rm MAX} \\ ({\rm GHz}) \end{array}$ | $\begin{array}{c} \mathrm{BV}_{\mathrm{CEO}} \\ \mathrm{(V)} \end{array}$ |

|------------------|-------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------|

| [20] 2013        | 0.8 x 6                                   | 400                                                     | 350                                                       | -                                                                         |

| This work        | $0.7 \ge 5$                               | 267                                                     | 450                                                       | 7.5                                                                       |

| [21] 2001        | $0.5 \ge 8$                               | 171                                                     | 425                                                       | 8                                                                         |

| [22] 2015        | $0.5 \ge 6$                               | 290                                                     | 320                                                       | $\approx 4$                                                               |

| [23] 2016        | $0.2 \ge 4.4$                             | 495                                                     | 882                                                       | 4.1                                                                       |

| [24] 2015        | $0.18 \ge 2.7$                            | 404                                                     | 901                                                       | 4.3                                                                       |

reduce charging times and access resistances and capacitances and thus increase device  $f_{MAX}$  [19]. The scaling rule for InP based DHBTs derived in [19] predicts a 2:1 bandwidth increase for a 4:1 decrease in emitter width, assuming that also the vertical dimensions are consequently scaled. Based on this assumption, the InP DHBT design presented in this work show a high potential when compared to other published results as presented in Table 1.2. It is evident, however, that further performance improvement of the devices presented in this work will need an effort toward device scaling to smaller emitter widths.

# 1.3 Objectives of this work

The work done in this thesis is part of the EU Marie Curie ITN EID<sup>1</sup> project "InP DHBT Optimization for Mm-wave Power Applications" (IN-POWER). Starting from the previous generation of InP DHBT fabricated at III-V Lab for high-speed mixed-signal applications [25], the goal of this work is to adapt the existing transistor technology to the design of power amplifiers targeting E-band and higher frequencies. For power amplification (PA) applications, the

<sup>&</sup>lt;sup>1</sup>Initial Training Network European Industrial Doctorate

maximum oscillation frequency  $f_{MAX}$  and breakdown voltage  $BV_{CEO}$  of the DHBT are considered two critical figures of merit (FOM) to improve in order to maximize circuit performance. In particular, the objective of this project is to provide InP DHBTs with  $f_{MAX}$  approaching 500 GHz and  $BV_{CEO}$  above 7 V maximizing at the same time the power cell output power by using multiple devices combined in parallel.

This thesis is structured as follows:

**Chapter 2**: this chapter is organized in three parts and focuses on the selection of the single-finger device for the PA power cell. In the first section the single-finger InP DHBT technology developed at III-V Lab is presented along with the static and high-frequency performances with respect to different layout dimensions. In the second section a 2D TCAD physical simulation approach is presented including a discussion about different models suitable for InP DHBTs. Finally, a discussion about device collector structure design is presented.

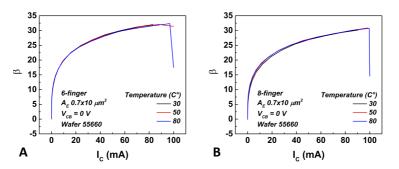

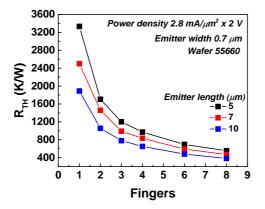

**Chapter 3**: this chapter is focused on the selection of a multi-finger device to increase the output power of the PA power cell. Firstly, the static and high-frequency characterization of InP multi-finger DHBTs is reported. Then the thermal characterization of the devices from electrical measurements is presented. In addition, a 3D TCAD thermal simulation approach is described and validate against measurements. Finally, the results from thermal characterization and simulations are used to improve the large-signal model of multi-finger DHBTs for SOA simulations.

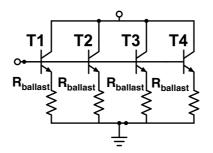

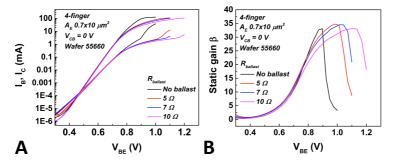

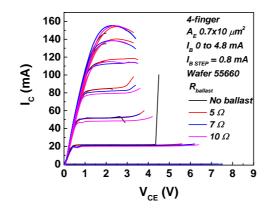

**Chapter 4**: in this chapter, different approaches to improve device SOA are introduced focusing on the concept of ballasting resistors. Different ballasting networks are compared in terms of static and high-frequency performances. A modeling approach for ballasted devices is discussed based on EM simulation of passive structures and on the physical modeling with lumped circuit elements. Finally the performances of multi-finger DHBTs in common-base configuration are presented.

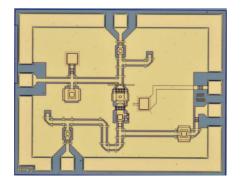

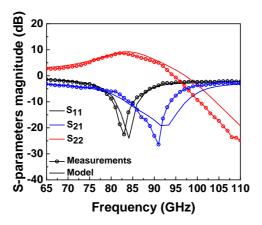

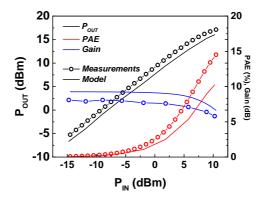

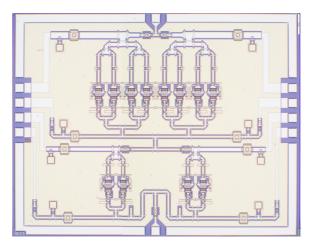

**Chapter 5**: Chapter 5 presents a small selection of PA mm-wave circuits designed and measured by other researchers involved in the IN-POWER project. The objective of this chapter is to briefly showcase the capability of the InP DHBTs selected in this thesis when used within a PA circuit.

# Chapter 2

# Single finger InP DHBT optimization

# 2.1 Baseline device structure

## **Epitaxial structure**

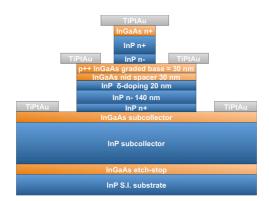

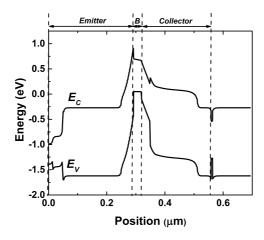

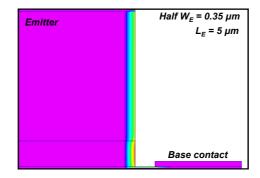

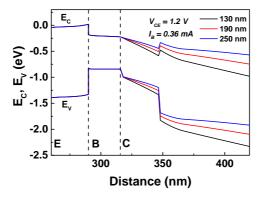

The majority of HBTs including the devices discussed in this work, are fabricated according to a triple-mesa structure. The operation of the device is mainly determined by the properties of the different layers in the vertical structure grown in the epitaxy process. For the DHBTs fabricated at III-V Lab, materials are grown by Gas Source Molecular Beam Epitaxy on a 3" semi-insulating InP substrate. The structure consists of a 40 nm InP emitter, a  $\approx 30$  nm highly C-doped and compositionally graded InGaAs base and a composite collector. The collector includes a non-intentionally doped (nid) InGaAs spacer, a highly doped InP region and a low doped InP layer. A low-doped InP layer is used to fully deplete the collector at low bias. A simplified structure description of the device is shown in Fig. 2.1 while Fig. 2.2 shows the equilibrium band diagram of a InP/InGaAs DHBT device. The emitter contact structure includes In<sub>0.85</sub>Ga<sub>0.15</sub>As highly n-doped cap layer to reduce emitter resistance and InP highly n-doped layer. The base layer is very thin to minimize the base transit

Figure 2.1: Schematic cross-section view and simplified layer structure of a single finger InP DHBT (with 190 nm total collector thickness).

time. It is also highly carbon doped ( $\approx 8 \times 10^{19} \text{ cm}^{-3}$ ) in order to decrease the base sheet resistance to a value of roughly 800-900  $\Omega/\Box$ . The doping level is chosen high enough to obtain a low total base resistance and thus increase  $f_{MAX}$  while still allowing for a static gain  $\beta$  higher than 20.

The epitaxy optimization process includes the reduction of device self-heating effects occurring at high dissipated power levels. As the thermal conductivity of InGaAs is considerably lower than InP, the general approach consists in thinning of InGaAs layers [26]. In particular, the InGaAs subcollector layer is thinned to roughly 5 nm. Besides improving device thermal behavior, the subcollector layer is still thick enough to provide its function as collector contact layer and to behave as an etch-stop layer in the fabrication process.

The results presented in this thesis are based on devices from wafers with different collector thicknesses, as listed in Tab. 2.1. As it will be explained in more detail in Sec. 2.4.3, in order to obtain the desired performances devices with different collector structures were considered including a low doped  $n^-$  layer of different thickness. It is worth mentioning, however, that due to a certain degree of variance concerning the epitaxial and technological fabrication process, even devices having the same epitaxial structure but measured on different wafers may exhibit slightly different performances. For all the measurements results presented throughout the thesis it will be specified the corresponding wafer on which the measurements were performed.

## Fabrication process

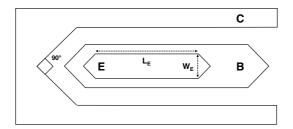

The DHBTs with an hexagonal shape [25] are fabricated using a wet-etch triple mesa technology including a self-aligned emitter-base metallization technique.

Figure 2.2: Equilibrium energy band diagram of an InP/InGaAs DHBT.

Table 2.1: List of wafers and corresponding collector dimensions for fabricated devices in this work.

|       | Total collector thickness (nm) |

|-------|--------------------------------|

| 55656 | 190                            |

| 55660 | 190                            |

| 55657 | 130                            |

| 54608 | 250                            |

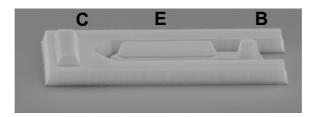

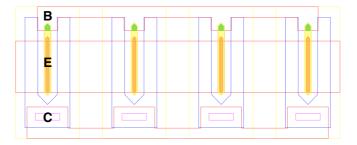

In this process the functional parts of the DHBT corresponding to emitter, base and collector result in three separate mesas one on top of the other after etching the epitaxial structure described in the previous section. Figure 2.3 presents the sideview of a single-finger transistor indicating the location of emitter, base and collector contact.

The transistor is typically designed to be emitter-up because this configuration leads to easier fabrication process for high-speed applications [27] however collector up designs have also been demonstrated by other labs [28].

Figure 2.4 shows the simplified layout of a triple-mesa HBT including relevant geometrical parameters as emitter width  $W_E$  and length  $L_E$ . The width of the emitter contact is 0.7  $\mu$ m (effective emitter width is approximately 0.6  $\mu$ m ). The base contact extends 0.3  $\mu$ m on each side of the emitter and includes a plug for the connection. Both contacts are defined by electron beam lithography because of the high alignment precision required for this technology. Other process steps are realized using stepper lithography. The collector contact also includes a plug for connection. TiPtAu is used for all contacts. After encapsulation with SiN and planarization with polyimide, emitter, base and collector contacts are opened by etching to interconnect the devices.

Figure 2.3: Sideview SEM photo of a single-finger DHBT including contact metallization and showing Emitter (E), Base (B) and Collector (C) contacts.

In order to select the most suitable device for the PA power-cell design, single-

Figure 2.4: Top view simplified schema of a triple-mesa HBT device with hexagonal shape.

finger DHBTs with different emitter layout geometries were investigated in this work. In particular, measured devices included all the combinations of emitter width W<sub>E</sub> equal to 0.5, 0.7, 1 and 1.5  $\mu$ m and emitter length L<sub>E</sub> equal to 5, 7, 10  $\mu$ m.

# 2.2 Characterization of single-finger DHBT

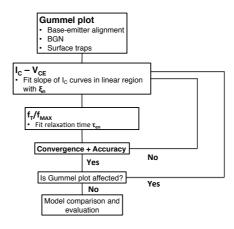

In order to assess the functionality and the performances of the different singlefinger DHBTs, static and frequency measurements were carried out for each emitter geometry on wafer 55656 available in the beginning of the project. The static measurements include especially Gummel plot and I<sub>C</sub> -V<sub>CE</sub> curves. The investigation of the frequency performances relies instead on small-signal Sparameters measurements taken at different bias points.

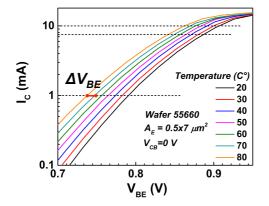

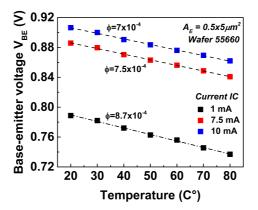

## 2.2.1 Static results

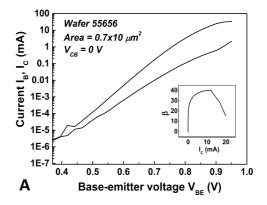

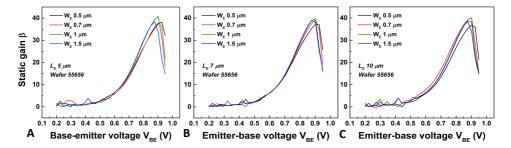

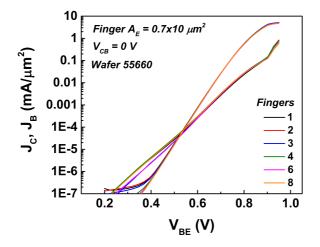

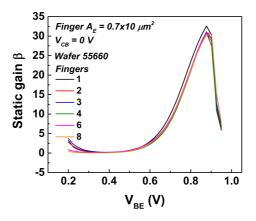

The first static characterization method is Gummel plot measurements. During measurements, the device is biased with an increasing emitter-base voltage  $V_{BE}$  while keeping the base-collector voltage  $V_{BC} = 0$  V. The base current  $I_B$  and the collector current  $I_C$  are plotted on a logarithmic scale as a function of  $V_{BE}$ . The forward static gain  $\beta$  in common-emitter configuration is computed by the ratio of  $I_C$  over  $I_B$ . In the ideal case the  $I_B$  and  $I_C$  curves would be parallel over the whole range of  $V_{BE}$  and consequently  $\beta$  would stay constant. In real devices, for low current levels base recombination currents become predominant while series resistance, thermal effects and the occurrence of Kirk effect lead to collector current saturation and base current increase. The effect of all of these non-idealities can be seen from a plot of the gain  $\beta$  that increases towards a peak value followed by a continuous drop. Figure 2.5 presents the Gummel plot of a 0.7x10  $\mu$ m<sup>2</sup> single finger device and the corresponding static current gain ( $\beta$ ) versus collector current ( $I_C$ ) with a peak value around 40.

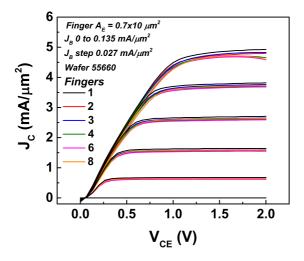

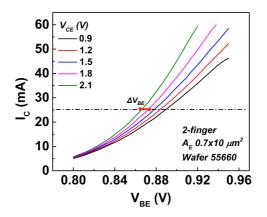

For the DHBT optimization for high-frequency application a very high static gain is not of paramount importance but a value above 20 is considered the minimum for practical functionality. In addition to the above mentioned nonideality factors, the geometry of the device affects the magnitude of the parasitic recombination currents and thus the static performance. Lateral dimensions such as emitter width  $W_E$  and length  $L_E$  directly influence the parasitic surface recombination currents. In order to avoid the predominance of these effects, it is therefore important to keep a high ratio between the device active area and its periphery. For the InP DHBTs discussed in this work, the effect of device dimension on the static gain was investigated for the available geometries. Figures 2.6 shows a plot of the static gain  $\beta$  vs. base-emitter voltage V<sub>BE</sub> for representative devices with different emitter dimensions. It is immediately clear that for each of the three cases the values of the gain peak values are very close to each other and do not show a clear trend with respect to a geometrical parameter. The average value for the ensemble of the measured devices is 38 with a standard deviation of 1.4. It was concluded that the static gain can be considered mainly independent on device geometrical dimensions. In order to obtain device I-V curves, the collector current  $I_{\rm C}$  is measured as a function of collector-emitter voltage  $V_{CE}$  while biasing the device at different  $I_B$  (in common-emitter configuration). The final result is a set of curves corresponding to the function  $I_{C} = f(V_{CE}, I_{B})$  where  $I_{B}$  is a stepped parameter.

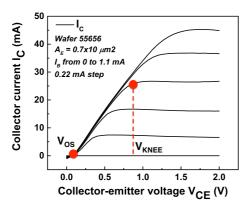

Although the I-V curves measurements are not used as a direct tool to select the optimal geometry for a single-finger in the power cell, they are employed as a diagnostic tool and to assess the static performance of the devices. Important parameters that can be inferred from the I-V curves are the offset voltage  $V_{OS}$  and the knee voltage  $V_{KNEE}$ . The former corresponds to the value of  $V_{CE}$  for which the collector current is equal to zero when a I<sub>B</sub> is forced while the latter is

Figure 2.5: Gummel plot and static current gain  $\beta$  of a single-finger DHBT with emitter area 0.7x10  $\mu$ m<sup>2</sup>.

Figure 2.6: A) Static gain  $\beta$  vs base-emitter voltage V<sub>BE</sub> for devices with emitter length L<sub>E</sub> equal to A) 5, B) 7 and C) 10  $\mu$ m and different emitter widths.

the  $V_{\rm CE}$  value for which the collector current has reached almost its maximum value in the linear region. Figure 2.7 shows the output characteristic curves from the measurements of collector current versus collector-emitter voltage up to 2 V for different values of base current  $I_{\rm B}$  from 0 to 1.1 mA with a 0.22 mA step for a single-finger DHBT with 0.7x10  $\mu m^2$  emitter area. The values of  $V_{\rm OS}$  and  $V_{\rm KNEE}$  are also indicated on the graph.

## 2.2.2 High-frequency results

The high-frequency performances of the devices were determined from smallsignal scattering parameters (or S-parameters) measurements. The measurements are performed over the frequency range from 250 MHz to 110 GHz using an Anritsu VectorStar Vector Network Analyzer (VNA). The VNA is calibrated

Figure 2.7:  $I_{\rm C}$  (V $_{\rm CE}$ ) curves of a single-finger 0.7x10  $\mu m^2$  DHBT. The base current I\_{\rm B} is varied from 0 to 1.1 mA with a 0.22 mA step.

using an off-wafer calibration kit. During the measurements the transistors are biased with different collector current values and fixed collector-emitter  $V_{CE}$ voltage. On-wafer dummy structures are included for each transistor geometry in order to de-embed the additional parasitic elements generated by the contact pads from measured data. The de-embedding method is based on a three-step Open-Short procedure as described in [29]. From the measured S-parameters the device small-signal current gain  $h_{21}$  can be computed according to:

$$h_{21} = \frac{-S_{21}}{(1 - S_{11})(1 - S_{22}) + S_{12}S_{21}}$$

(2.1)

Mason's unilateral power gain U can be computed as:

$$U = \frac{\left|\frac{S_{21}}{S_{12}} - 1\right|^2}{2\left(k\left|\frac{S_{21}}{S_{12}}\right| - Re\left(\frac{S_{21}}{S_{12}}\right)\right)}$$

(2.2)

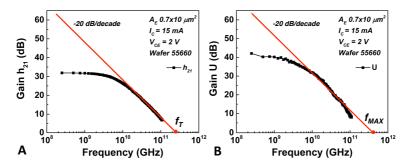

The two quantities  $h_{21}$  and U are plotted vs. frequency for each bias point. By definition  $f_T$  and  $f_{MAX}$  are the frequencies for which  $h_{21}$  and U become equal to 0 dB. Thus the values of  $f_T$  and  $f_{MAX}$  are extrapolated by fitting a -20dB/decade line to experimental  $h_{21}$  and U data in the high-frequency range. Fig. 2.8 illustrates the extrapolation of  $f_T$  and  $f_{MAX}$  on de-embedded data of a 0.7x10  $\mu$ m<sup>2</sup> DHBT biased at  $I_C = 15$  mA and  $V_{CE} = 2$  V. From Fig. 2.8 it can be seen that the fitting of the - 20 dB/decade line in logarithmic scale not extremely accurate for Mason's gain U. As a consequence, a certain degree of uncertainty exists for the extraction of  $f_{MAX}$  value.

Figure 2.8: Extrapolation of  $f_{\rm T}$  and  $f_{\rm MAX}$  from A)  $\rm h_{21}$  and B) U for a 0.7x10  $\mu m^2$  DHBT. The bias point is I\_{\rm C} = 15 mA, V\_{\rm CE} = 2 V.

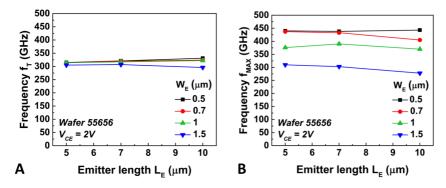

According to the procedure described above, the high-frequency performances of single-finger DHBTs with different emitter sizes were considered in order to extract their  $f_T$  and  $f_{MAX}$  operating frequencies. Fig. 2.9 presents values of  $f_T$ and  $f_{MAX}$  of single finger transistors having emitter length of 5-7-10  $\mu m$  and emitter width of 0.5-0.7-1-1.5  $\mu m$  . Reported  $f_T$  and  $f_{MAX}$  values refer always to the frequency peak value reached by increasing collector current  $I_{\rm C}$  at  $V_{\rm CE}$ = 2 V before a drop off due to Kirk effect. In Fig. 2.9-A it can be seen that the cutoff frequency shows at most 10% variation with respect to device geometrical scaling and is only slightly larger for devices with smaller emitter width. Fig. 2.9-B shows that emitter geometrical dimensions have a stronger influence on measured  $f_{MAX}$  values. In particular,  $f_{MAX}$  approaches 450 GHz for devices with  $W_E$  of 0.5-0.7  $\mu m$  while it is reduced by 30% to 300 GHz for devices with  $W_E = 1.5 \ \mu m$ . From Eq. 2.3 it can be seen that the cutoff frequency depends directly on device lateral dimensions through the RC products related to the emitter layers and junction  $R_E$  and  $C_{je}$ . Since the resistor and capacitance terms have inverse dependence on device area,  $f_{\rm T}$  in theory should be independent on emitter area. However, due to 2D and border effects the scaling of model parameters may not be exactly proportional to emitter area scaling. In addition, a contribution exist related to cross-products between the emitter resistance and the base-collector capacitance that do not scale proportionally to emitter area. The terms related to base-collector capacitance are distributed between intrinsic and extrinsic capacitance  $C_{\rm bci}$  and  $C_{\rm bcx}$  with the former related to device active area and (thus proportional to emitter area) and the latter dependent mainly on base mesa dimension thus constant in our case.

From the data reported so far DHBTs with emitter widths of 0.5 or 0.7  $\mu$ m were selected to be suitable candidates for the unit power cell. As stated in the project objectives, output power is considered an important criteria so the final choice has to take into account the maximization of the transistor active area. In this sense, single-finger DHBT having W<sub>E</sub> =0.7  $\mu$ m offered a good trade-off

Figure 2.9: Peak cutoff frequency  $f_{\rm T}$  (A) and  $f_{\rm MAX}$  (B) as a function of  $L_{\rm E}$  for devices with different emitter width  $W_{\rm E}$  from 0.5 to 1.5  $\mu m$ .

between frequency performance and device active area.

In the following of this section, additional measurements results concerning the high-frequency performances of single-finger DHBTs with  $W_E = 0.7 \ \mu m$  will be presented. Moreover the parameters of the small-signal model of a 0.7x10  $\ \mu m^2$  DHBT are introduced.

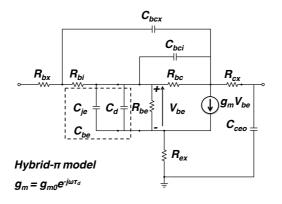

With respect to the hybrid topology representation of the small-signal model shown in Fig. 2.10 the cutoff frequency  $f_T$  is defined as:

$$\frac{1}{2\pi f_T} = \tau_b + \tau_c + r_E (C_{je} + C_{BC}) + (R_E + R_C) C_{BC}$$

(2.3)

where the extracted  $\tau_{\rm b}$  and  $\tau_{\rm c}$  are the base and collector transit time respectively, r<sub>E</sub> is the dynamic base-emitter resistance divided by the current gain  $\beta$ , C<sub>BC</sub> is the total base-collector capacitance, C<sub>je</sub> is the base-emitter junction capacitance, R<sub>E</sub> and R<sub>C</sub> are the extrinsic emitter and collector resistance, respectively. According to the approximate expression:

$$f_{MAX} \approx \sqrt{\frac{f_t}{8\pi (R_{bx}(C_{bcx} + C_{bci}) + R_{bi}C_{bci})}}$$

(2.4)

$f_{max}$  is optimized by reducing the product of the extrinsic and intrinsic base resistance ( $R_{bx}$  and  $R_{bi}$ ) and base-collector capacitance ( $C_{bcx}$  and  $C_{bci}$ ).

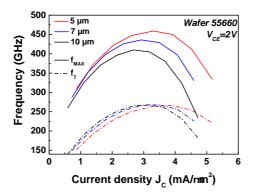

Figure 2.11 presents the extracted  $f_T$  and  $f_{MAX}$  vs.  $J_C$  ( $V_{CE} = 2 V$ ) for single finger devices with emitter length 5, 7, 10  $\mu$ m and emitter width 0.7  $\mu$ m.

The 5  $\mu$ m length device exhibits highest values with  $f_T = 267$  GHz and  $f_{MAX} = 450$  GHz at  $J_C \approx 3.5 \text{ mA}/\mu\text{m}^2$ . As a further validation of the trends presented earlier for the previous wafer, increasing the emitter length from 5 to 10  $\mu$ m,  $f_T$  remains constant while  $f_{MAX}$  decreases to 410 GHz for a peak current density of  $J_C \approx 3 \text{ mA}/\mu\text{m}^2$ . From these results, a device with contact emitter size 0.7x10

Figure 2.10: Hybrid- $\pi$  small-signal equivalent model.

Figure 2.11:  $f_{\rm T}$  and  $f_{\rm MAX}$  versus J $_{\rm C}$  for 0.7  $\mu{\rm m}$  emitter width DHBTs with emitter lengths of 5,7 and 10  $\mu{\rm m}$  .

$\mu m^2$  is then selected because it has the largest active device area while offering frequency performances sufficiently high for the PA power cell. Although the wafer epitaxial structures are nominally the same, the peak  $f_T$  values for DHBTs with  $W_E = 0.7 \ \mu m$  reported in Fig. 2.11 are lower than the ones reported in Fig. 2.9 having the same dimensions. In particular, the peak  $f_T$  is equal to 320 GHz for  $0.7 \times 10 \ \mu m$  DHBTs from wafer 55656 while it is around 270 GHz for the same devices on wafer 55660. Two reasons exist causing this difference related to unwanted variation of the technological and epitaxial process. Firstly, a higher degree of emitter mesa underetching exists for devices from Fig. 2.11 causing a reduction of device active area and thus an increase of the emitter resistance. This leads to a higher R-C product in Eq. 2.3. The second reason is the fact that the lightly n-doped layer in the collector of devices from wafer 55656 is probably thinner, leading to a shorter transit time in the collector.

| Table 2.2: Small-signal model parameters of single-fir | iger DHBTs with W $_{ m E}$ =0.7 $\mu{ m m}$ and L $_{ m E}$ = 5,10 $\mu{ m m}$ . The |

|--------------------------------------------------------|---------------------------------------------------------------------------------------|

| model is extracted at $I_{\rm C}$ equal to 6.5 mA ar   | nd 15 mA for L $_{ m E}$ equal to 5 $\mu{ m m}$ and 10 $\mu{ m m}$ , respectively     |

| and $V_{\rm CE}$ =2V.                                  |                                                                                       |

|                                                        |                                                                                       |

| $egin{array}{llllllllllllllllllllllllllllllllllll$ | $\mathbf{R}_{\mathrm{bi}}$ ( $\Omega$ )  | $f R_{ m be}\ (\Omega)$    | $egin{array}{c} \mathbf{C}_{\mathrm{be}} \ \mathbf{(fF)} \end{array}$ | $f R_{ m bc}$ ( $\Omega$ )                                         | $egin{array}{c} \mathbf{C}_{\mathrm{bci}}\ \mathbf{(fF)} \end{array}$ | $egin{array}{c} \mathbf{C}_{\mathrm{bcx}} \ \mathbf{(fF)} \end{array}$ |

|----------------------------------------------------|------------------------------------------|----------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|

| 5<br>10                                            | $\begin{array}{c} 20\\ 10.9 \end{array}$ | $190.5 \\ 111$             | $78.3 \\ 154.4$                                                       | $280.7 \\ 172.6$                                                   | $1.84 \\ 5$                                                           | $4.5 \\ 4.24$                                                          |

|                                                    | $\mathbf{R}_{\mathrm{e}}$ ( $\Omega$ )   | $f R_{ m bx}$ ( $\Omega$ ) | $\mathbf{R}_{\mathrm{cx}}$ ( $\Omega$ )                               | $egin{array}{c} \mathbf{C}_{	ext{ceo}}\ \mathbf{(fF)} \end{array}$ | $egin{array}{c} {f g}_{ m m0} \ {f (S)} \end{array}$                  | $	au_{ m d}$ (ps)                                                      |

| 5<br>10                                            | $4.7 \\ 2.4$                             | $4.28 \\ 5.38$             | $19.3 \\ 10.9$                                                        | $\begin{array}{c} 6.8 \\ 6.8 \end{array}$                          | $184.6 \\ 323$                                                        | $0.43 \\ 0.45$                                                         |

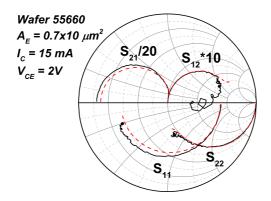

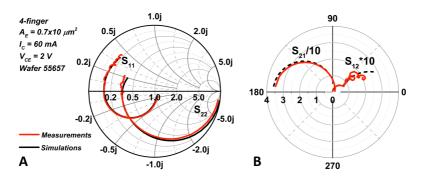

In order to further investigate the frequency behavior of the devices, the hybrid-  $\pi$  small-signal model components of a devices with W<sub>E</sub> = 0.7  $\mu$ m and L<sub>E</sub> =5,7,10  $\mu$ m have been extracted from S-parameters measurements following the procedure described in [30]. The model parameters are extracted at the bias point that corresponds to the peak f<sub>MAX</sub> value, that is at I<sub>C</sub> =15.5 mA for a 0.7x10  $\mu$ m<sup>2</sup> device and to I<sub>C</sub> =15 mA for 0.7x5  $\mu$ m<sup>2</sup> DHBT. The applied bias voltage is V<sub>CE</sub> = 2 V in both cases. Table 2.2 summarizes the numerical values extracted for the small-signal model in the two cases. The S-parameters of the extracted model are then simulated in ADS in the same frequency range and the comparison with the measured S-parameters show a good agreement as shown in Fig. 2.12 only for a 0.7x10  $\mu$ m<sup>2</sup> emitter DHBT.

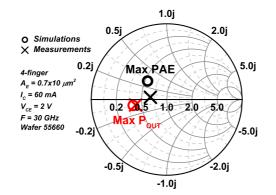

Large signal performance of a 0.7x10  $\mu$ m<sup>2</sup> InP DHBT were investigated at 30

Figure 2.12: Measured (250 MHz-110 GHz) and simulated S-parameters of a 0.7x10  $\mu m^2$  single-finger DHBT at bias point I\_C =15 mA, V\_{\rm CE} =2V.

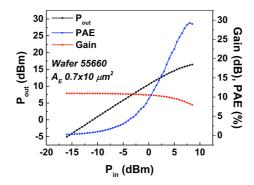

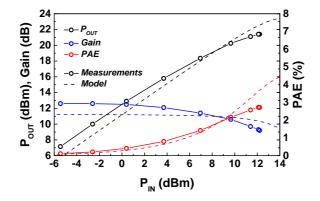

GHz, which was the maximum operating frequency of the available load-pull test bench. The bias point was selected for Class A operation, corresponding to  $(V_{CE}, I_C) = (2 \text{ V}, 15 \text{ mA})$  for a single-finger device. In measurements, the access pad structure has not been de-embedded, so the values of the optimum loads take into account the contribution of such a structure, and the considered power levels are those present at the probe tips. The optimum load selected in order to obtain maximum output power is  $Z_L = 58.15 + j15.3 \Omega$ . From the  $P_{IN}$ - $P_{OUT}$  plot

Figure 2.13: Measured power sweep for a 0.7x10  $\mu m^2$  single finger InP DHBT at 30 GHz. The device is biased in Class A with V\_{\rm CE} =2 V and I<sub>C</sub> =15 mA. The impedance value for maximum P<sub>out</sub> is equal to Z<sub>L</sub>=58.15 + j15.3  $\Omega$ .

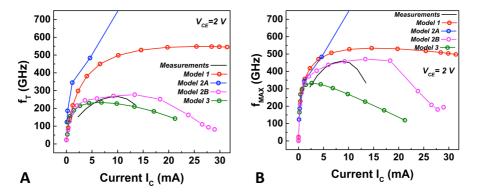

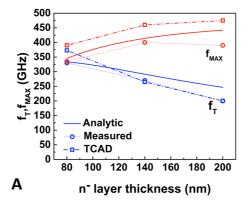

of Fig. 2.13, it can be seen that the saturated output power of the single-finger device is around 15 dBm and the small-signal gain is higher than 14 dB, while the power added efficiency is higher than 25% for a collector thickness of 190 nm. Once the emitter geometry is identified based on high-frequency measurements, the vertical structure is further investigated for collector optimization. In addition to measurements, a TCAD model of a DHBT was realized as an aid to evaluate high-frequency performances of different structures in terms of  $f_{\rm T}$  and  $f_{\rm MAX}$ . In the rest of the chapter the details of the TCAD model will be presented and the simulation results will then be compared to static and high-frequency measurements.

## 2.3 TCAD physical model

One way to accelerate the device design cycle and obtain useful insights for the future generations of fabricated devices is to employ an accurate TCAD physical model. In particular for this work, the main objective was to implement a predictive TCAD model that could be used to investigate the frequency performances of InP DHBTs with different collector structures. Many relevant publications exist pertaining HBT simulations based on SiGe [31] and InP materials [32]. For InP based HBT simulations mostly single heterojunctions have been considered. Published works concerning InP DHBTs are less numerous. The modeling of carrier transport in DHBT devices proves to be difficult due to a more complex collector structure and carrier velocity relationship with electric field. Previous published works exist regarding simulation of InP DHBTs with InGaAs [33] and GaSbAs base[34][35]. TCAD simulations were employed to investigate device non-idealities and reliability issues concerning the interaction between electrical and thermal mechanisms [36][37][32]. The work in [33] represents probably the most complete reference in which also limited complexity circuits are simulated starting from the physical model. Although being inspired by the approach in [33], we were not able to easily replicate the results because the collector structure is somehow different and because of different commercial software employed. Other published results reach different levels of agreement compared among them and with respect to measurement results. In particular, they often present a very well modeled specific issue of a devices without showing how the model behaves with different simulation conditions (i.e. bias point, frequency range...) and device structures. We found that the lack of an extensive presentation of the model in different conditions might indicate the over-fitting of some model parameters and the presence of numerical convergence problems in other conditions. In this work, an attempt was made to avoid of overfitting of model parameters in order to guarantee the flexibility of simulation for a wide frequency range and different bias conditions.

## 2.3.1 Simulation environment

#### Structure definition

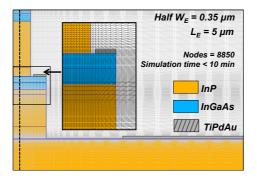

The geometry of the structure is described in terms of the epitaxial layer stack with the corresponding layout dimensions of the triple-mesa process. The default simulation results are computed for a 2D section of the device and a third dimension can be defined in the perpendicular out-of-plane direction only as a scaling factor. Taking advantage of the intrinsic symmetry of the device and physical mechanisms involved, only half of the device structure was simulated in order to reduce computational time. Calibration simulations showed that it is possible to reduce the number of simulated nodes by eliminating portions of the peripheal layers in the horizontal and vertical dimension while introducing a negligeable error. For example, the original substrate thickness was reduced from 300  $\mu$ m to 80  $\mu$ m and the width of the collector mesa was reduced from 4.4  $\mu$ m to 2.2  $\mu$ m to obtain the final simulation structure of Fig. 2.14. This reduces

Figure 2.14: 2D section of a simulated single finger InP DHBT with 0.7 μm emitter width. Only half of the real structure is simulated to exploit intrinsic symmetry and reduce computational time.

also the number of nodes that are present in inactive parts of the simulated structure as in the insulating layer. To each region is assigned the corresponding material including the surrounding medium. Special regions in the structure are defined to be the electrodes to which current and voltages are applied during simulations Fig. 2.14 also shows the cutline along which all the relevant 1D results will be presented in the next sections.

#### Meshing

The 2D simulation domain was carefully meshed to avoid numerical error and inaccuracies at the heterojunctions and at the interface between semiconductor and insulating material. The CPU time required for simulation is proportional to N<sup> $\alpha$ </sup> where N is the number of nodes and  $\alpha$  varies between 2 and 3 according to the complexity of the problem. Thus the best practice is to define a mesh fine enough in critical regions to converge to a correct solution and coarser in the rest of the structure. For the DHBT simulation problem, a straight rectangular mesh was defined without iterative refining and optimization during simulation runtime. As can be seen in Fig. 2.15 the meshing domains are finer and do not contain obtuse triangle in the vertical domain corresponding to device active area and where strong electric field exist. In the outer regions corresponding to the passivation material, these conditions are not respected but the convergence of the solution is not compromised as the electric field and conduction in this domain is practically zero. For vertical bipolar devices and in particular for HBTs the most important meshing recommendations are:

• define an adequate meshing density in zones where a high electric field is expected such as in the collector region.

- avoid obtuse triangles along the current path or in high electric field region.

- generally avoid abrupt meshing transitions. This sort of discontinuities may also cause the existence of obtuse triangles. In addition, meshing has to be finer for frequency simulation as more resolution is needed for spatial variation of the electric field under small-signal excitation. Static simulation can be performed with a coarser mesh definition but in this work the same mesh was defined both for static and high-frequency simulations. This increases the simulation time for DC simulations but ensures the consistency with the static operating point computing during small-signal parameters simulations.

Figure 2.15: 2D section of a simulated single finger InP DHBT including meshing of the structure.

## 2.3.2 Material parameters

The 2D physical simulation of devices including III-V materials is performed using the hydrodynamic approach in order to correctly take into account effects occurring at the heterojunctions. A careful selection of material parameters related to InP and  $In_{0.53}Ga_{0.47}As$  and parameters related to the calibration of empirical models is required. A few parameters are available in the commercial version of the simulation software while most of the values are available in previously published works. Material parameters include electron effective mass, dielectric permittivity and band diagram parameters. Many material parameters are not constant and depend on material properties like doping and device operating conditions like applied electric field and temperature. These dependencies are described by empirical models present in literature and included in the simulations. Table 2.3 summarizes the values used in this work. The emitter cap layers, the base and the subcollector layer are heavily doped at levels exceeding the nominal value of conduction band effective density of states and are thus degenerate semiconductors. In this case, the parabolic band

|                                                          | InP                 | $\mathrm{In}_{0.53}\mathrm{Ga}_{0.47}\mathrm{As}$ |

|----------------------------------------------------------|---------------------|---------------------------------------------------|

| Bandgap (eV)                                             | 1.35                | 0.75                                              |

| Affinity (eV)                                            | 4.38                | 4.59                                              |

| Electron effective mass $\left(\frac{m_e^2}{m_0}\right)$ | 0.08                | 0.0463                                            |

| Hole effective mass $\left(\frac{m_h^*}{m_o}\right)$     | 0.6                 | 0.432                                             |

| Nc $(cm^{-3}eV^{-1})$                                    | $5.8 \cdot 10^{17}$ | $2.8 \cdot 10^{17}$                               |

| $Nv (cm^{-3}eV^{-1})$                                    | $1.1 \cdot 10^{19}$ | $9.10^{18}$                                       |

|                                                          |                     |                                                   |

Table 2.3: Material parameters at T=300 K used for device simulation of InP DHBTs in this work

approximation fails and this leads to erroneous simulation results in which the Fermi level reaches too deep within the conduction band. This issue is taken into account by applying the model presented in [38] to compute the relative electron effective mass  $m_e^*$  and then the electron effective density of states  $N_c$  using a third order polynomial formula.

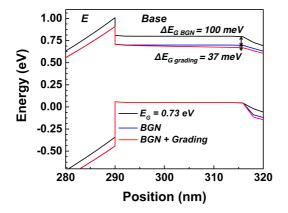

#### Bandgap narrowing (BGN)

Due to the high doping level of the base and of the cap layers ( $\approx 10^{19}$ ) the energy band gap of InP and InGaAs decreases and also the electron affinity value is influenced. This effect has to be included in the simulation because it strongly affects the energy band diagram at the heterojunction interface. The approach used to compute the amount of BGN and its distribution between conduction and valence band is based on the model of Jain-Roulston [39] and is presented in [40]. This numerical model allows to calculate the amount of reduction of energy gap due to doping N distributed between conduction and valence band according to:

$$\Delta E_c^{BGN}(N) = C_1 \left(\frac{N}{10^{18}}\right)^{\frac{1}{\alpha}} + C_2 \left(\frac{N}{10^{18}}\right)^{\frac{1}{2}}$$

(2.5)

$$\Delta E_v^{BGN}(N) = C_3 \left(\frac{N}{10^{18}}\right)^{\frac{1}{\beta}} + C_4 \left(\frac{N}{10^{18}}\right)^{\frac{1}{2}}$$

(2.6)

with  $\Delta E_g^{BGN} = \Delta E_c^{BGN} + \Delta E_v^{BGN}$  and the parameters used in the simulation are presented in [40] for InP/InGaAs abrupt HBTs. In the case of In<sub>0.47</sub>Ga<sub>0.53</sub>As with  $\approx 6 \cdot 10^{19}$  donor doping, the amount of BGN is around 100 meV and

$\Delta E_c^{BGN} \approx 35 \text{ meV}$  and  $\Delta E_v^{BGN} \approx 65 \text{ meV}$ .

#### Graded base

The concentration of Gallium with respect to Indium in the base is varied from 52.5% to 47% from the emitter to the collector side. This compositional grading introduces an additional narrowing of the energy diagram of the base layer decreasing from emitter to collector. This introduces an quasi-electric field that accelerates electrons in addition to the diffusion mechanism. From previous studies on the same technology [41], the variation of energy bandgap estimated from the emitter to collector side of the base layer is between 30 and 40 meV. The combined effect of doping related BGN and compositional grading is that the energy band gap in the base is approximately 630 meV at the collector side and between 660 and 670 meV at the emitter side. The height of the conduction band spike is approaches 200 meV at the emitter-base junction as illustrated in Fig. 2.16.

In Fig. 2.16, the energy band diagram of the base layer used for TCAD

Figure 2.16: Effect of Bandgap Narrowing and compositional grading on the energy bandgap profile in the base layer taken into account in TCAD simulations.

simulations is shown when the default InGaAs  $E_G$  is used and when BGN and compositional grading effects are taken into account. The reduction of  $E_G$  at the collector side in the base with respect to the default value is of 100 meV and 37 meV for BGN and grading respectively.

# 2.3.3 Recombination models

For the correct simulation of DHBT current gain, recombination mechanisms need to be taken into account in different layers including recombination due to bulk traps and surface traps. Regarding bulk traps recombination, three physical mechanisms are taken into account for 2D simulations: Shockley-Read-Hall (SRH), Auger and radiative recombination.

#### Bulk and surface SRH

SRH recombination rate  $R^{SRH}$  is computed for every layer according to:

$$R^{SRH} = \frac{np - n_i^2}{\tau_p \left( n + n_i e^{\frac{E_T}{k_B T}} \right) - \tau_n \left( p + n_i e^{\frac{-E_T}{k_B T}} \right)}$$

(2.7)

where  $\tau_n$  and  $\tau_p$  are electron and hole lifetimes respectively and  $E_T$  is the trap energy level with respect to the valence (conduction) band for donors (acceptors). Starting from the results of previously published works based on the same technology [37], recombination centers are assumed to be located at mid gap and and since  $n \gg p$  in the emitter layer,  $\tau_n$  and  $\tau_p$  are assumed to have the same value.  $\tau_n$  and  $\tau_p$  are both set to 1 ns for InP and to 1 ns and 5 ns for InGaAs.

#### **Radiative recombination**

Radiative recombination is taken into account in every layer according to:

$$R^{rad} = C^{rad} \left( np - n_i^2 \right) \tag{2.8}$$

where the coefficient  $C^{rad}$  is set to  $6.6 \cdot 10^{-11}$  for InP and  $1.4 \cdot 10^{-10}$  for InGaAs.

#### Auger recombination

For doping levels higher than  $10^{19}$  Auger recombination mechanism becomes dominant especially in the InGaAs base layer. Auger recombination rate can be

computed using the following equation:

$$R^{Auger} = C_n^{Auger} \left( pn - nn_i^2 \right) + C_p^{Auger} \left( pn - pn_i^2 \right)$$

(2.9)

Auger recombination coefficients for InGaAs are usually in the range  $10^{-30}$ - $10^{-28}~{\rm cm}^6/{\rm s}$  and were set to  $C_n^{\rm Auger}{=}5{\cdot}10^{-30}$  and  $C_p^{\rm Auger}{=}3{\cdot}10^{-29}$  based on recombination current measurements.

#### Surface traps

Surface traps (ST) are surface defects of the semiconductor lattice caused for example by missing interface atoms and have strong influence on device electrical performance. From the energy point of view, STs are located within the forbidden material bandgap and can contribute to carrier capture and emission according to SRH model. The impact of surface defects needs to be included in DHBTs simulations in order to obtain a good correlation with the static experimental results concerning Gummel plot and output characteristics. In a DHBT triple-mesa structure, it was shown that traps mostly critical for device simulation are located on the emitter lateral sidewall and on the base ledge between emitter and base contact as shown in Fig.2.17.

The main parameters to define in the simulation models are the location of the

Figure 2.17: Location of surface traps at emitter sidewall and base ledge for device simulation.

surface traps, the trap density and energy level and the capture cross-section. The values used in this work are based on [42] and [37], although some slight modification in trap energy level has to be applied between different devices to better fit the base current in Gummel plot. Table 2.4 summarizes the parameters for surface trap implemented in ATLAS.

| Material | Missing atom     | Type of trap                  | $\rm E_{T}$ - $\rm E_{V}$               | ST density                                                                                 |

|----------|------------------|-------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------|

| InP      | In<br>P          | Donor<br>Acceptor             | $\begin{array}{c} 1.2 \\ 1 \end{array}$ | $rac{N_{T}}{N_{T}}$                                                                       |

| InGaAs   | In<br>Ga<br>As   | Donor<br>Donor<br>Acceptor    | $0.61 \\ 0.24 \\ 0.36$                  | $\begin{array}{c} 0.53 \times N_{\rm T} \\ 0.47 \times N_{\rm T} \\ N_{\rm T} \end{array}$ |

|          | N <sub>T</sub> i | s equal to $3 \times 10^{12}$ | 2                                       |                                                                                            |

Table 2.4: Parameters for surface trap model

# 2.3.4 Transport models

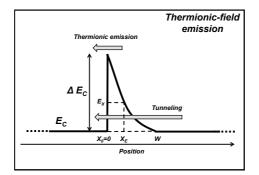

#### Heterojunction current transport

The interface between the InP emitter and the InGaAs base and between the InGaAs spacer and the InP collector of a DHBT is an abrupt heterojunction. Carriers' flow is controlled by two main physical mechanisms involved shown schematically in Fig. 2.18:

- Thermionic emission of electrons *over* the emitter-base barrier

- Tunnel effect *through* the emitter-base spike

Figure 2.18: Schematic illustration of physical mechanism for carrier transport at heterojunction

The carrier transport between the two regions is described by the *thermionic field-emission* model that takes into accounts both effects [43]:

$$J_n = q v_{Tn} (1+\delta) (n_E - n_B e^{\frac{-\Delta E_c}{k_B}})$$

(2.10)

where  $J_n$  is the electron current density and  $v_{Tn}$  is the electron thermal velocity. The superscript E and B denotes the emitter and base region. The parameter  $\delta$  accounts for the contribution of the tunneling current and can be calculated from:

$$\delta = \frac{1}{kT} \int_{E_{min}}^{E_C^E} e^{\left(\frac{E_c^E - E_x}{kT}\right)} e^{\left(\frac{-4\pi}{h} \int_0^{X_E} [2m^*{}_n(E_C - E_x)^{0.5}] dx\right)} dE_x$$

(2.11)

where  $E_{\min} = max[E_C(0^-), E_C(W)]$  and  $E_x$  is the energy component in the x direction as described in Fig. 2.18 for the case  $E_{\min} = E_C(0^-) = E_C(W)$ The thermal velocity is defined as:

$$w_{Tn} = \frac{A_n^* T_L^2}{qN_c}$$

(2.12)

where  $T_L$  is the lattice temperature,  $N_c$  is the electron effective density of states in the emitter and  $A_n^*$  is the effective Richardson constant. For simulations, it is sufficient to consider bias points with  $V_{BE} > 0.75$  V as this is often the region of operation of the device. Since the height of the emitter-base spike is quite reduced for this bias, the thermionic emission is the dominant effect at the emitter base junction while tunneling could be neglected. The thermionic field-emission model is not activated at collector-base junction.

#### Energy balance model

Starting from Boltzmann transport equation two transport models can be derived:

- Drift-Diffusion (DD)

- Energy Balance (EB) and its simplified form Hydrodynamic Model (HD)

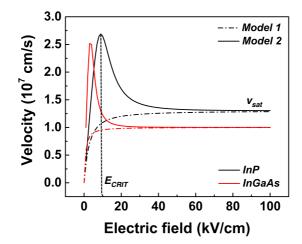

The DD transport model is the simplest from the conceptual and numerical point of view. The main advantage is that the only independent variables are electron and holes concentration n and p and the potential  $\phi$ . Despite being the most popular transport model for device simulation, it can lead to erroneous results for submicron InP DHBT. Indeed it does not take into account important phenomena as *hot electrons* that occur in devices with submicron dimensions. On the other hand, the EB and HD models are more advanced and include additional variables to be explained later, leading to more accurate physical results. The trade-off between DD and EB models comes in the form of additional simulation time and added difficulty to converge of the resolution algorithm. The

EB model follows from a simplified form of the Boltzmann transport equation according to Stratton derivation [44]. The HD model is further derived from the EB model by changing suitable parameters as it will be described in the next sections. In the EB model two additional variables are added to the systems of equations already defined for the DD model. These variables are the electron and holes temperatures (related to their respective energies) defined as  $T_n$  and  $T_p$  respectively. A new term is added to the current density expressions:

$$J_n = qD_n\nabla n - qn\mu_n\nabla\psi + qnD_n{}^T\nabla T_n$$

$$J_p = qD_p\nabla p - qp\mu_p\nabla\psi - q + pD_p{}^T\nabla T_p$$

(2.13)

where  $D_n^T$  and  $D_p^T$  are coefficients of thermal diffusion. In addition to third term in Eq.2.13, the concept of *energy flux density* between carriers and lattice is introduced for electrons and holes as  $S_n$  and  $S_p$ , respectively. These terms are described as:

$$S_{n} = -K_{n} \nabla T_{n} - \left(\frac{k_{B}\delta_{n}}{q}\right) J_{n}T_{n}$$

$$\nabla \cdot S_{n} = \frac{J_{n}E}{q} - W_{n} - \frac{3k_{B}}{2} \frac{\partial(nT_{n})}{\partial t}$$

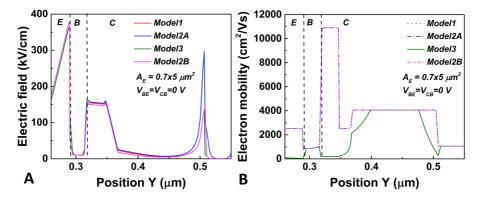

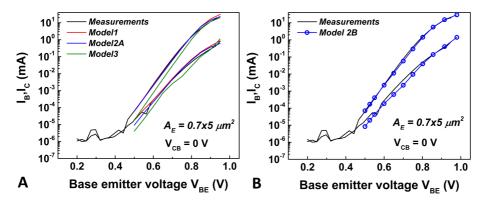

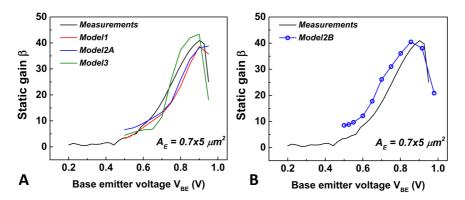

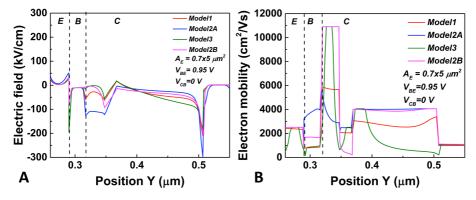

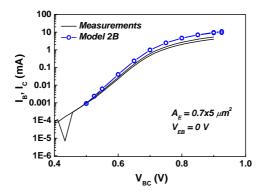

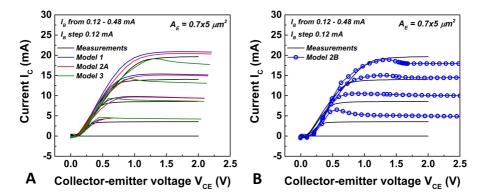

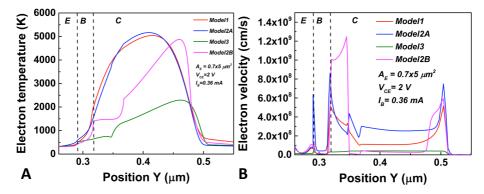

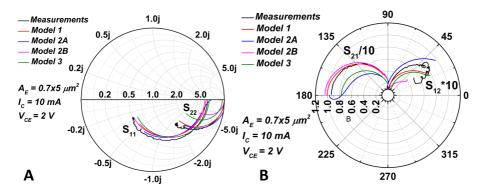

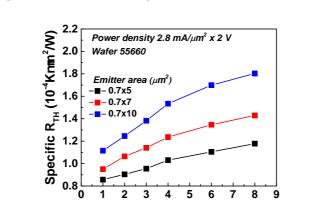

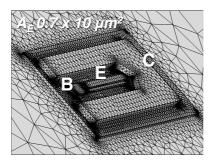

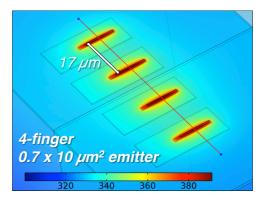

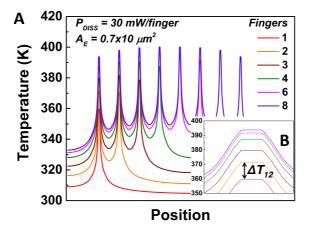

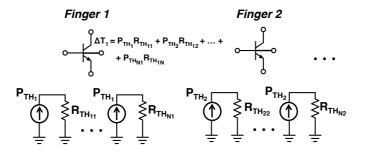

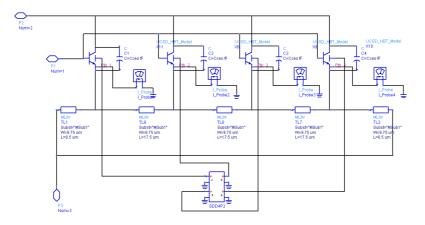

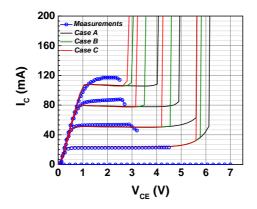

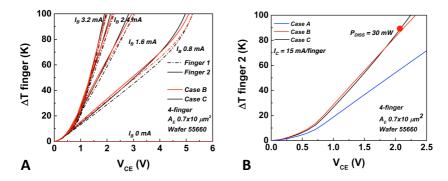

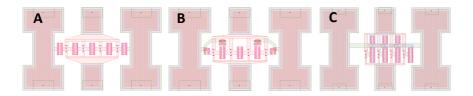

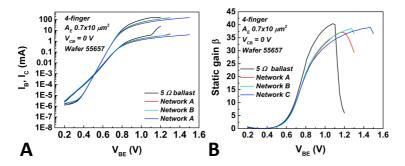

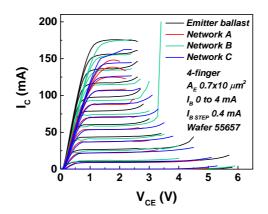

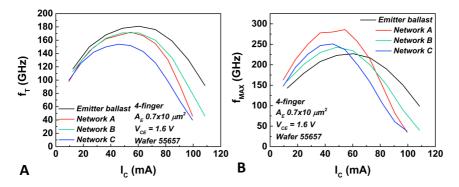

$$S_{p} = -K_{p} \nabla T_{p} - \left(\frac{k_{B}\delta_{p}}{q}\right) J_{p}T_{p}$$